Методы производства КНИ-структур

Известно, что переход от кремниевых пластин, в том числе с эпитаксиальным

слоем, на КНИ-структуры при производстве большого

класса полупроводниковых приборов и микросхем дает заметные преимущества по

сравнению с объемным материалом и, в частности, снижение потребляемой мощности

и увеличение быстродействия. Для производства СБИС используются два основных

метода изготовления КНИ-пластин (зарубежное название SiliconOnInsulator–

SOI):

·имплантационный метод – внедрение в глубину

кристалла ионов кислорода (SiliconImplantedbyOxygen–

SIMOX) с последующим синтезом скрытого оксида при высокотемпературном

(> 1300°С) отжиге;

·прямое сращивание (бондинг)

облученной водородом донорной окисленной пластины

кремния с опорной подложкой с последующим почти полным удалением донорной пластины путем ее скалывания

имплантированным водородом (метод водородного переноса кремния с оксидом Smart-Cut SOI ).

В Институте физики полупроводников СО РАН в 1996-2001 гг. была

разработана технология, обеспечившая возможность экономически эффективного

производства в России высококачественных структур КНИ для микроэлектроники.

Технология, названная “DeleCut” (hydrogenirradiatedDeletedoxideCutting), является вариантом метода Smart

Cut. На технологию DeleCut

получен Российский патент , изучается также возможность ее патентования в

США.

В технологии изготовления КНИ-пластин DeleCut, объединяющей методы гидрофильного соединения и

водородного отслоения , устранены недостатки прототипа. Соответствие

различных методов изготовления КНИ-пластин

требованиям СБИС-технологии с проектными нормами 0,1 мкм отражено в табл. 1. Главным достоинством запатентованного метода

DeleCut является структурное и электрофизическое

совершенство границы сращивания, находящейся между слоем перенесенного кремния

и скрытым термическим оксидом Si/SiO2, что

позволило получать слои монокристаллического кремния и оксида толщиной до

3 нм. Метод DeleCut опробован также при создании

структур кремний-на-кремнии, перспективных для

изготовления силовых приборов и упорядоченных массивов квантовых точек.

Таблица 1. Сравнительные оценки пригодности КНИ-пластин, изготовленных разными методами, для проектной

нормы 0,1 мкм

|

Параметр |

Метод |

Примечания |

|||

|

SIMOX |

Smart-cut |

ELTRAN |

DeleCut |

||

|

Толщина слоя Si 30-100 нм |

хор. |

хор. |

удовл. |

отл. |

Имплантация и окисление |

|

Разброс толщины Si ±5% |

отл. |

хор. |

хор. |

отл. |

Нет проблем на |

|

Плотность дислокаций ≤ 5·104 см-2 |

удовл. |

удовл. |

удовл. |

удовл. |

ОДУ характерны |

|

Плотность HF-дефектов ≤ 1 см-2 |

плохо |

плохо |

хор. |

плохо |

SIMOX ITOX и ELTRAN |

|

Плотность ВОХ-дефектов (Seco) ≤ 1 см-2 |

плохо |

хор. |

отл. |

отл. |

Включения частиц Si для SIMOX является критическим |

|

Шероховатость Si/BOX ≤ 1 нм |

плохо |

хор. |

хор. |

отл. |

Шероховатый интерфейс для Si/SiO2 в SIMOX и атомно |

|

Плотность ВОХ-дефектов (GOI) ≤ 1 см-2 |

удовл. |

хор. |

отл. |

отл. |

Исходное качество |

|

Пригодность для |

удовл. |

хор. |

удовл. |

чор. |

КНИ Smart |

|

Основные недостатки |

Низкий выход, высокие |

Мягкая полировка, |

Гидролиз, эпитаксия |

HF-дефекты |

Расходящиеся по методам технологии, |

По технологии DeleCut изготовлены

экспериментальные партии КНИ-пластин диаметром

76-150 мм с бездислокационными КНИ-слоями толщиной от 0,01 до 1,8 мкм со скрытым

термическим оксидом SiO2 (0,05-1,9 мкм). Показано, что

полученные КНИ-пластины обладают высокими

электрофизическими характеристиками, пригодными для создания КМОП СБИС, СВЧ

БИС, оптоэлектронных приборов и различных сенсоров (давления, температуры,

излучения) .

Оптоэлектронные ключи, актюаторы и сенсоры на КНИ-структурах

КНИ-структуры давно привлекали внимание

разработчиков оптоэлектронных и микроэлектромеханических

систем (МЭМС). Большая разница в оптических коэффициентах

преломления для Si и SiO2 (6,55 и 1,46 для

лазера на парах иода при 383; 3,44; 1 мкм, для светодиодов с эрбием при мкм) и низкие потери в волноводах (0,1 дБ/см) делают эту

систему универсальной для большинства оптоэлектронных приложений: мультиплексоров,

демультиплексоров, триггеров, усилителей и

электрически управляемых дифракционных решеток (см

например, обзор ).

В отличие от волноводов на стекле, использование диапазона 1,3-1,6 мкм

делает высокопроизводительные волноводные схемы полностью совместимыми с

существующими КМОП СБИС и УБИС.

Огромная разница в скоростях избирательного травления для Si и SiCO2 (до 106) и

совместимость с высокоразрешающей интегральной МОП-технологией

упрощают методы создания МЭМС. Особенно перспективны для этих двух приложений

многослойные КНИ-структуры, поскольку они открывают

прямой путь к трехмерной интеграции в оптоэлектронных и микросистемных

устройствах .

Отличительная особенность сенсоров на КНИ-структурах

– низкий уровень шумов в широком диапазоне рабочих температур. Накопленный в

ИФП СО РАН опыт разработки и создания датчиков давления, газовых потоков и

температур на КНИ-структурах показал также

возможность двух – трехкратного увеличения эксплуатационных диапазонов

сенсорных устройств. Возможность их интеграции с операционными усилителями,

ЦАТТ и АЦП на КНИ-структурах позволяет разрабатывать

уникальные кремниевые “песчинки”, способные автономно собирать информацию о

параметрах окружающей среды в труднодоступных местах и в экстремальных условиях

и передавать ее в “интеллектуальные” сети сенсоров и актюаторов

.

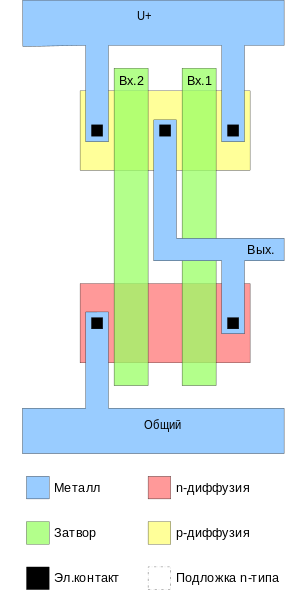

Логические КМОП (КМДП) элементы «И»

Схема логического элемента «И-НЕ» на КМОП микросхемах практически совпадает с упрощенной

схемой «И» на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что

нагрузка подключается не к общему проводу схемы, а к источнику питания. Это формирует инверсию выходного сигнала. Принципиальная

схема логического элемента «2И-НЕ», выполненного на комплементарных МОП

транзисторах (КМОП или КМДП), приведена на рисунке 3.

«2И-НЕ»

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор,

однако при формировании низкого уровня сигнала схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки

используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать

высокий потенциал, то транзисторы открываются, а если низкий — то закрываются.

Обратите внимание, что КМОП топология логического элемента «2И-НЕ» получается еще проще. В качестве нижних двух полевых

транзисторов используется единый n канал, на котором формируется два затвора (двухзатворный полевой транзистор)

Упрощенная

топология логического элемента «2И-НЕ» на комплементарных МОП транзисторах приведена в и показана на

рисунке 4.

«2И-НЕ»

«2И-НЕ»

Такая топология позволяет занимать на кристалле интегральной микросхемы минимальное место и получать максимальную

плотность логических элементов. Способом, подобным приведенному на рисунке 4 легко могут быть получены логические

элементы «3И-НЕ», «4И-НЕ», «8И-НЕ» и т.д.

В приведённой на рисунке 3 схеме логического КМОП-элемента «2И-НЕ», ток от источника питания на выход

КМОП-микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу)

будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах логического КМОП-элемента

«И» будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе

КМОП микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме, приведенной на рисунке 1,

если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом

состоянии ток КМОП-микросхемой от источника питания потребляться не будет.

Условно-графическое изображение КМОП логического элемента «2И-НЕ»

не отличается от УГО ТТЛ, ДТЛ или ЭСЛ логических элементов и показано на рисунке 5, а таблица истинности

приведена в таблице 1. В таблице 1 входы обозначены как x1 и x2, а выход —

F.

Так что же ограничивает размера техпроцесса?

- Аппаратно-технологическая. Связана с разрешением аппаратуры.

- Физика техпроцессов. Определяется физическими ограничениями конкретного техпроцесса, который можно обойти сменой технологии или материалов.

- Физические. Это ограничения, которые обойти нельзя, но можно минимизировать их влияние.

- Предельные физические.

EUV-литография

EUV-литографияsic!В чем причина такого неприятия?неooops!Так выглядит EUV-сканер от ASMLРезультаты моделирования Монте-Карло путешествия электрона в кремнии с энергией в 20 и 5 эВ. Источник

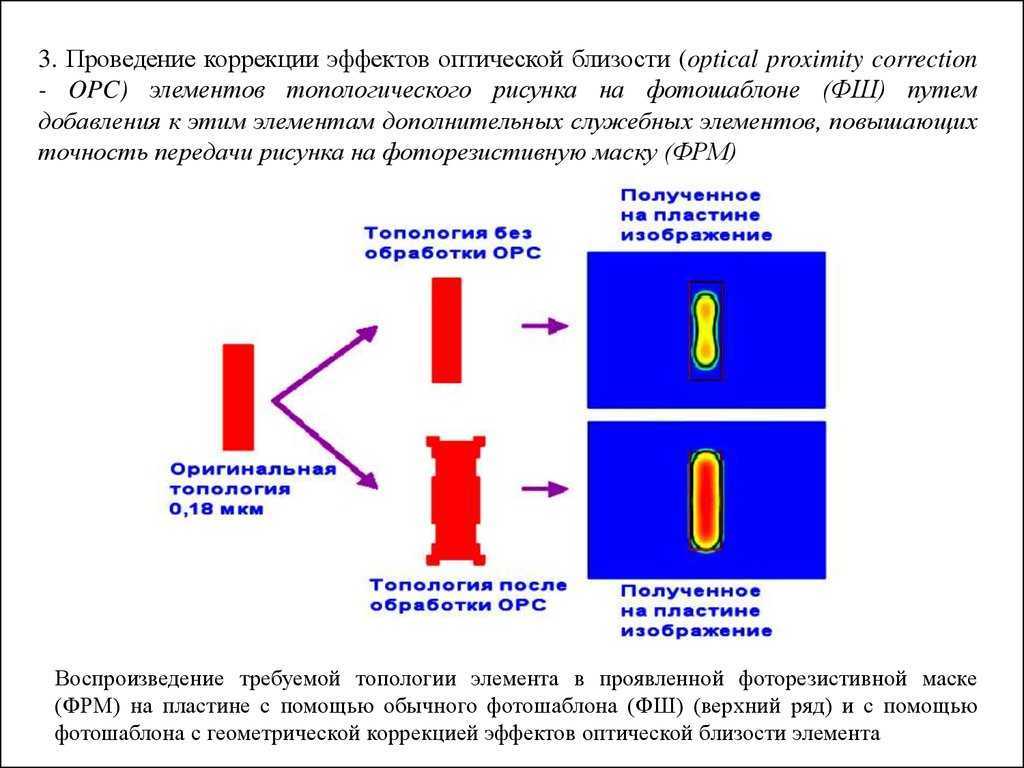

Есть и другие способы борьбы с дифракцией…

Коррекция оптической близости. Использование фазосдвигающих масок.интерференцииВнеосевое освещение.Многократное экспонирование.Фото первого слоя металлизации для 24 нм технологии. Слева создано 193 нм литографией, справа экспериментальной 13,5 нм (EUV). Как видим, от прежних четких прямоугольных форм остались только воспоминания. Тем не менее работает.во второй частиблог

Использование фазосдвигающих масок.интерференцииВнеосевое освещение.Многократное экспонирование.Фото первого слоя металлизации для 24 нм технологии. Слева создано 193 нм литографией, справа экспериментальной 13,5 нм (EUV). Как видим, от прежних четких прямоугольных форм остались только воспоминания. Тем не менее работает.во второй частиблог

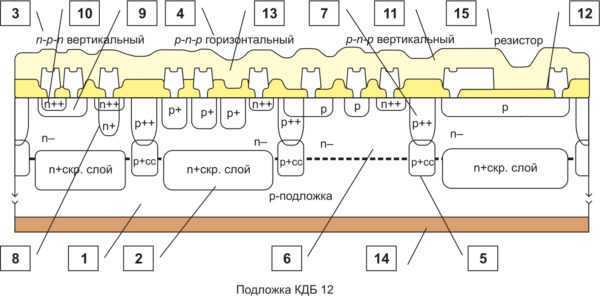

Биполярные технологии изготовления интегральных схем

Исторически первой технологией для производства микросхем силовой электроники была биполярная технология с изоляцией p-n-переходом, которая обеспечила пробивное напряжение Uкэ транзистора не менее 40 В. На рис. 3 представлен вертикальный срез типовой полупроводниковой структуры биполярной силовой интегральной схемы. Показаны в обобщенном виде активные структуры наиболее широко используемых в микросхемах элементов — вертикальных n-p-n-транзисторов, вертикального и горизонтального p-n-p-транзисторов, резисторов, а также конструкции изолирующих и «скрытых» слоев n+— и p+-типа проводимости. Наличие в структуре двух типов конструктивной реализации транзисторов p-n-p (вертикальной и горизонтальной) обуславливает возможность реализации широкого диапазона их усилительных свойств.

Рис. 3. Типовая структура фрагмента силовой интегральной схемы, изготовленной по биполярной технологии с изоляцией p-n-переходом

Рассмотрим последовательность выполнения технологических операций для структуры, представленной на рис. 3, без детализации режимов проведения этих операций. В высокоомной подложке p-типа проводимости 1 методом диффузии (сурьмы или мышьяка) формируют n+-скрытый слой 2, который предназначен для уменьшения сопротивления коллекторных областей вертикальных n-p-n-транзисторов 3 и базовых областей горизонтальных p-n-p-транзисторов 4. Необходимо отметить, что наличие высоколегированного n+-слоя позволяет уменьшить коэффициент усиления неизбежно возникающих в этой структуре «паразитных» p-n-p-транзисторов (на подложку). Удельное сопротивление n+ скрытого слоя лежит в диапазоне 10–30 Ом/кВ. Вместо объемного удельного сопротивления rv удобнее пользоваться поверхностным удельным сопротивлением rs. Связь между ними будет понятна из рассмотрения следующего соотношения, которое определяет сопротивление какого-либо слоя:

R = rvl/S = rvl/bh = rsl/b = rsn, (1)

где l — длина проводящей области; S — поперечное сечение проводящей области; b — ширина проводящей области; h — глубина проводящей области; n — число квадратов.

В дальнейшем методом диффузии бора создают p+-скрытый слой 5, который используется для лучшей электрической изоляции элементов друг от друга. Далее наращивают эпитаксиальную пленку 6 n-типа проводимости толщиной (15±1,5) мкм (для обеспечения Uкэ ≥ 40 В процесса) и rv = (4,5±0,45) Ом·см. Для легирования эпитаксиальной пленки используются сурьма или мышьяк из-за их низкой диффузионной способности. Затем методом диффузии бора формируют слой разделения 7. Хорошая изоляция элементов достигается при наличии контакта с p+-скрытым слоем.

Область глубокого коллектора 8 транзисторов n-p-n-типа создается методом диффузии фосфора. Эта область должна достичь области n+-скрытого слоя для уменьшения величины последовательных сопротивлений тела коллектора n-p-n-транзистора и базы p-n-p-транзистора.

Область базы 9 формируется методом диффузии или ионного легирования бора. Область эмиттера 10 формируется методом диффузии или ионного легирования фосфора.

На получившейся полупроводниковой структуре вскрываются контакты к областям в окисле 11. Затем методом напыления формируется металлизированная разводка 12 AlSi (1%) толщиной 1–3 мкм. Большая толщина необходима для более мощных приборов с целью уменьшения плотности тока в дорожках металлизации. Допустимая плотность тока — 2×105А/см2 (для низковольтных интегральных схем) или 5×105А/см2 (для приборов, имеющих неорганическое покрытие).

Завершается процесс изготовления созданием пассивирующего покрытия (окисла) 13 — НТФСС (низкотемпературное фосфоро-силикатное стекло).

Для снижения величины теплового сопротивления RТкр–кор мощных силовых приборов проводится утонение пластины с 460 до 350 мкм (для пластин диаметром 100 мм) механической шлифовкой обратной стороны пластины. Кроме того, если при сборке в корпус используется посадка кристалла на пайку, то на обратную (непланарную) сторону пластины наносят металлизацию 14 (Ti/W/Ag).

Рассмотренный процесс ориентирован на создание n-p-n-транзисторов. Транзисторы р-n-р-типа и другие элементы формируются из областей n-p-n-транзисторов 3. Горизонтальный р-n-р-транзистор 4 формируется на основе слоя p-базы n-p-n-транзистора. Резисторы 15 могут формироваться на основе слоя p-базы n-p-n-транзистора или отдельным слоем.

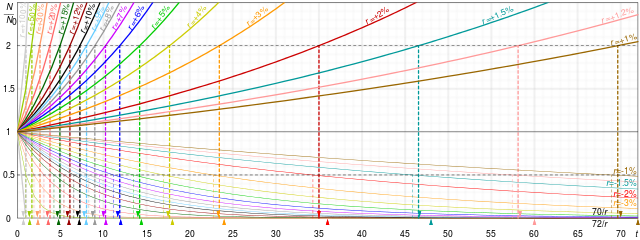

Основная формула

Количество Икс экспоненциально зависит от времени т если

- Икс(т)=а⋅бтτ{ Displaystyle х (т) = а cdot b ^ {т / тау}}

где постоянная а начальное значение Икс,

- Икс()=а,{ Displaystyle х (0) = а ,,}

постоянная б положительный фактор роста, а τ это постоянная времени — время, необходимое для Икс увеличить в один раз б:

- Икс(т+τ)=а⋅бт+ττ=а⋅бтτ⋅бττ=Икс(т)⋅б.{ displaystyle x (t + tau) = a cdot b ^ { frac {t + tau} { tau}} = a cdot b ^ { frac {t} { tau}} cdot b ^ { frac { tau} { tau}} = x (t) cdot b ,.}

Если τ > 0 и б > 1, тогда Икс имеет экспоненциальный рост. Если τ < 0 и б > 1, или же τ > 0 и 0 б < 1, тогда Икс имеет экспоненциальный спад.

Пример: Если количество бактерий удваивается каждые десять минут, начиная с одной бактерии, сколько бактерий будет присутствовать через час? Вопрос подразумевает а = 1, б = 2 и τ = 10 мин.

- Икс(т)=а⋅бтτ=1⋅2(60 мин)(10 мин){ displaystyle x (t) = a cdot b ^ {t / tau} = 1 cdot 2 ^ {(60 { text {min}}) / (10 { text {min}})}}

- Икс(1 час)=1⋅26=64.{ displaystyle x (1 { text {hr}}) = 1 cdot 2 ^ {6} = 64.}

Через час или шесть десятиминутных интервалов будет шестьдесят четыре бактерии.

Многие пары (б, τ) из безразмерный неотрицательное число б и количество времени τ (а физическое количество который может быть выражен как произведение количества единиц на единицу времени) представляют одну и ту же скорость роста, причем τ пропорционально бревнуб. Для любых фиксированных б не равно 1 (например, е или 2) темп роста задается ненулевым временем τ. Для любого ненулевого времени τ скорость роста определяется безразмерным положительным числомб.

Таким образом, закон экспоненциального роста может быть записан в различных, но математически эквивалентных формах, используя разные основание. Наиболее распространены следующие формы:

- Икс(т)=Икс⋅еkт=Икс⋅етτ=Икс⋅2тТ=Икс⋅(1+р100)тп,{ displaystyle x (t) = x_ {0} cdot e ^ {kt} = x_ {0} cdot e ^ {t / tau} = x_ {0} cdot 2 ^ {t / T} = x_ {0} cdot left (1 + { frac {r} {100}} right) ^ {t / p},}

где Икс выражает начальную величину Икс(0).

Параметры (отрицательные в случае экспоненциального спада):

- В постоянная роста k это частота (количество раз в единицу времени) роста в раз е; в финансах это еще называют логарифмической отдачей, непрерывно начисленная доходность, или же .

- В время электронного складывания τ время, необходимое для роста в раз е.

- В время удвоения Т время, необходимое для удвоения.

- Увеличение процента р (безразмерное число) за период п.

Количество k, τ, и Т, и для данного п также р, имеют взаимно однозначную связь, задаваемую следующим уравнением (которое может быть получено путем натурального логарифма приведенного выше):

- k=1τ=пер2Т=пер(1+р100)п{ displaystyle k = { frac {1} { tau}} = { frac { ln 2} {T}} = { frac { ln left (1 + { frac {r} {100}) } right)} {p}}}

где k = 0 соответствует р = 0 и до τ и Т быть бесконечным.

Если п это единица времени частное т/п это просто количество единиц времени. Используя обозначения т для (безразмерного) количества единиц времени, а не для самого времени, т/п можно заменить на т, но для единообразия здесь этого удалось избежать. В этом случае деление на п в последней формуле тоже не числовое деление, а преобразование безразмерного числа в правильное количество, включая единицу.

Популярным приближенным методом расчета времени удвоения по скорости роста является правило 70,то есть, Т≃70р{ displaystyle T simeq 70 / r}.

Графики, сравнивающие времена удвоения и периоды полураспада экспоненциального роста (жирные линии) и распада (слабые линии), а также их 70 /т и 72 /т приближения. в Версия SVG, наведите указатель мыши на график, чтобы выделить его и его дополнение.

Смещение экспоненциального роста

Исследования показывают, что людям сложно понять экспоненциальный рост. Смещение экспоненциального роста — это тенденция недооценивать сложные процессы роста. Эта предвзятость может иметь и финансовые последствия. Ниже приведены несколько историй, которые подчеркивают эту предвзятость.

Рис на шахматной доске

Согласно старинной легенде, визирь Сисса Бен Дахир подарила индийскому королю Шариму красивый ручной работы. шахматная доска. Король спросил, что он хотел бы взамен своего подарка, и придворный удивил короля, попросив одно зерно риса на первом квадрате, два зерна на втором, четыре зерна на третьем и т. Д. Король с готовностью согласился и спросил чтобы принести рис. Сначала все шло хорошо, но требование на 2п−1 зерна на п-й квадрат потребовал свыше миллиона зерен на 21-м квадрате, более миллиона миллионов (a.k.a. ) 41-го и риса во всем мире просто не хватило для последних квадратов. (Из Свирски, 2006 г.)

В вторая половина шахматной доски это время, когда экспоненциально растущее влияние оказывает значительное экономическое влияние на общую бизнес-стратегию организации.

Водяная лилия

Французским детям предлагается загадка, в которой показан аспект экспоненциального роста: «очевидная внезапность, с которой экспоненциально растущее количество приближается к фиксированному пределу». Загадка представляет собой растение водяной лилии, растущее в пруду. Растение удваивается в размерах каждый день, и, если его оставить в покое, оно задушит пруд за 30 дней, убив всех остальных живых существ в воде. День за днем рост растения невелик, поэтому решено, что это не будет проблемой, пока оно не покроет половину пруда. Какой это будет день? 29-й день, остается только один день на спасение пруда.

КНИ-структуры в технологии нанотранзисторов

Наиболее перспективными структурами для нанотранзисторов

также считаются КНИ-структуры. В мире разработано

несколько вариантов конструкций КНИ КМОП-нанотранзисторов.

Это классические транзисторы с планарным поликремниевым

затвором, транзисторы на ультратонких (до 10 нм) слоях кремния (UT SOI

MOSFET), транзисторы с планарным затвором (in-plan-gate— IPG), транзисторы с двойным

затвором (doublegate– DG), а также транзисторы,

использующие технологию опоясывающего затвора (gateallaround– GAA) для минимизации

последствий накопления заряда в скрытом оксиде, в том числе так называемые

“вертикальные” нанотранзисторы.

Использование КНИ-структур позволяет уменьшать

длину канала МОП-транзистора до 15 нм (см.

например ), а дизайн двойного затвора позволяет достичь длины канала

5-6 нм . В КНИ-транзисторе вклады квантовых

эффектов не являются доминирующими, и нанотранзистор

ведет себя подобно классическому субмикронному КМОП-транзистору кремниевой микроэлектроники. Этот подход

был опробован в ИФП СО РАН с использованием стандартной оптической литографии и

плазмохимии для достижения размеров менее 100 нм. Были разработаны,

изготовлены и исследованы характеристики тестовых полевых КНИ-транзисто-ров

и логических элементов с размерами около 100 нм. При толщине отсеченного

слоя кремния 100 нм и концентрации бора в нем 5·10 см-3

классические -канальные транзисторы имеют минимальную длину для

канала без смыкания менее 100 нм. В -канальных транзисторах минимальная длина канала без

смыкания около 200 нм. Транзисторы показывали классические характеристики

с крутизной около 100 и 120 мВ/дек для — и -канальных транзисторов соответственно без заметных “king”-эффектов. Токи утечек транзисторов существенно меньше

10 А при ширине канала 20 мкм .

Другим вариантом является переход к неклассическим конструкциям нанотранзисторов . В рамках этого направления в ИФП СО

РАН были разработаны, изготовлены и исследованы характеристики полевых КНИ-ланотранзисторов с латеральными затворами и размерами

элементов в нанометровом диапазоне . При толщине

отсеченного слоя кремния 5-50 нм длина канала транзистора уменьшалась до

40-50 нм. Электронная литография сфокусированным электронным пучком при

использовании высокомолекулярного полиметилметакрилата (и ) в

качестве резиста позволила изготовить планарные

кремниевые (КНИ) полевые транзисторы четырех конструкций. Были изготовлены нанотранзисторы на легированном слое кремния с одним и двумя

расщепленными латеральными затворами с минимальными размерами элементов до

20 нм (рис.1)

и на нелегированном канале с дополнительными затворами из титана или поликремния, лежащими над каналом поверх подзатворного оксида толщиной 10 нм (рис.2). Создание

дополнительных затворов потребовалось из-за чрезвычайно низких емкостей

латеральных затворов при использовании в качестве изолятора двуокиси кремния.

Приборы с латеральным затвором обладают прекрасными высокочастотными

характеристиками, однако для модуляции сильно легированных каналов требуются

напряжения на затворе в десятки и сотни вольт. Альтернативным вариантом для

литографического разрешения 10-20 нм является применение в качестве

изолятора диэлектриков с большой диэлектрической

постоянной (например, SrBaTiO3).

|

Рис. 1 |

Рис. 2 |

Переход к нанотранзисторам неизбежен для

дальнейшего прогресса в информационных технологиях, поскольку только на этом

пути в ближайшем будущем возможно изготовление терагерцовых

процессоров и терабитных схем памяти.

Семейства КМОП-микросхем

Первые КМОП-микросхемы не имели защитных диодов на входе, поэтому их монтаж представлял значительные трудности. Это

семейство микросхем серии К172. Следующее улучшенное семейство КМОП микросхем серии К176 получило эти защитные диоды.

Оно достаточно распространено и в настоящее время. Серия К1561 завершает развитие первого поколения КМОП микросхем. В

этом семействе было достигнуто быстродействие на уровне 90 нс и диапазон изменения напряжения питания 3 … 15В.

Так как в настоящее время распространена иностранная аппаратура, то приведу иностранный аналог этих КМОП микросхем —

C4000В.

Дальнейшим развитием КМОП-микросхем стала серия SN74HC. Эти микросхемы отечественного аналога не имеют. Они

обладают быстродействием 27 нс и могут работать в диапазоне напряжений 2 … 6 В. Они

совпадают по цоколёвке и функциональному ряду с ТТЛ микросхемами,

но не совместимы с ними по логическим уровням, поэтому одновременно были разработаны КМОП микросхемы серии SN74HCT

(отечественный аналог — К1564), совместимые с ТТЛ микросхемами и по логическим уровням.

В это время наметился переход на трёхвольтовое питание. Для него были разработаны КМОП-микросхемы SN74ALVC с временем

задержки сигнала 5,5 нс и диапазоном питания 1,65 … 3,6 В. Эти же микросхемы способны работать

и при 2,5 вольтовом питании. Время задержки сигнала при этом увеличивается до 9 нс.

Наиболее перспективным семейством КМОП-микросхем в настоящее время считается семейство SN74AUC с временем задержки

сигнала 1,9 нс и диапазоном питания 0,8 … 2,7 В. Прошу не путать дискретные микросхемы с ПЛИС и

микропроцессорами. Внутри таких микросхем задержка может быть меньше 0,3 нс.

Дата последнего обновления файла

15.04.2020

Спецификация топологического слоя

Каждый простейший геометрический элемент (многоугольник, прямоугольник, проводник) должен быть обозначен путем точного указания технологического фотошаблона, к которому он относится.

В формате CIF для спецификации слоя используется сокращенное наименование, а в формате GDSII — номер слоя (табл. 2). Наименования слоя или его номера используются в целях повышения четкости файла и для исключения необходимости согласования с многочисленными разработчиками и изготовителями БИС.

Таблица 2. Условное обозначение топологических слоев в формате GDSII и в CIF2,0 в масштабируемой КМОП-технологии

Промежуточная форма представления данных для описания топологии ИС

Промежуточная форма представления данных CIF2.0 (сокращение от «Caltech Intermediate form»), разработанная в Калифорнийском технологическом институте, является средством описания графических элементарных групп (характеристик фотошаблона). Файлы в форме CIF создаются средствами САПР (топологическими редакторами, например Ledit Tanner EDA) на базе других форм представления данных, таких как символический язык геометрической структуры. Идея, положенная в основу этой формы записи, состоит в литеральном описании каждого геометрического объекта с достаточной степенью точности.

Независимо от метода проектирования топологии, полученные проекты преобразуются в форму CIF, являющуюся промежуточной формой представления данных, перед следующей трансляцией проекта применительно к различным формам выходных устройств, таких как графопостроители, устройства генерации изображений.

КНИ-структуры для систем-на-чипе

Предполагается, что КНИ-структуры

найдут широкое применение в большинстве необходимых для практики сравнительно

недорогих однокристальных КНИ-микросистемах, ориентированных

на различные применения в любых климатических условиях, на относительно

невысокую при этом стоимость, высокую эффективность и надежность работы.

Отличительной особенностью таких микросистем будут интегрированные функции

оптической и радиосвязи и наличие интегрированных сенсоров и актюаторов .

Особенно перспективным, по нашему мнению, является использование в КНИ-структурах в качестве подложек пластин БЗП-кремния. Высокоомная БЗП-подложка в сочетании с декананометровым

приборным слоем, отсеченным от нее тонким скрытым оксидом, позволит производить

КНИ СБИС и УБИС типа систем-на-чипе со встроенным гигагерцовым радиоканалом для беспроводных сетевых

технологий.

История

Схемы КМОП в изобрёл Фрэнк Вонлас (Frank Wanlass) из компании Fairchild Semiconductor, первые микросхемы по технологии КМОП были созданы в . Долгое время КМОП рассматривалась как энергосберегающая, но медленная альтернатива ТТЛ, поэтому микросхемы КМОП нашли применение в электронных часах, калькуляторах и других устройствах с батарейным питанием, где энергопотребление было критичным.

К году с повышением степени интеграции микросхем встала проблема рассеивания энергии на элементах. В результате технология КМОП оказалась в выигрышном положении. Со временем была достигнута скорость переключения и плотность монтажа недостижимые в технологиях, основанных на биполярных транзисторах.

Ранние КМОП-схемы были очень уязвимы к электростатическим разрядам. Сейчас эта проблема в основном решена, но при монтаже КМОП-микросхем рекомендуется принимать меры по снятию электрических зарядов.

Для изготовления затворов в КМОП-ячейках на ранних этапах применялся алюминий. Позже, в связи с появлением так называемой самосовмещённой технологии, которая предусматривала использование затвора не только как конструктивного элемента, но одновременно как маски при получении сток-истоковых областей, в качестве затвора стали применять поликристаллический кремний. Это было вызвано тем, что алюминий не мог выдержать высокотемпературного процесса «разгонки» примеси, проводимой после получения стока и истока (типичная температура процесса — около 1000°С). Но в настоящее время наблюдается тенденция возвращения к металлическим затворам, для получения которых используются тугоплавкие металлы, выдерживающие высокие температуры. Уход от поликристаллического кремния вызван его неустранимым недостатком — высоким сопротивлением, которое снижает быстродействие схем.

Заключение

Если сравнить логический каскад ТТЛ и КМОП, а тем более N-МОП, то с коммерческой точки зрения выпускать аппаратуру с последним типом логики выгоднее. Тем более характеристики потребления и степени интеграции явно в сторону полевых транзисторов. К примеру, есть приборы, (например теплосчётчики «Струмень» и др.) работающие от аккумулятора. Его заряда хватает на несколько лет непрерывной эксплуатации. Однако есть аппараты (к примеру теплосчётчики ТЭМ-05, ТЭМ-104, ТЭМ-106 и др.) которым необходимо питание от сети с потреблением более 10Вт×ч.

Персональные компьютеры (ПК) в отличие от ноутбуков изначально предполагалось разграничить по принципу типа логики. ПК рассчитывались использовать в более влажных условиях, чем ноутбуки и планшеты, имеющие уклон компактности. Однако многие производители компонентов к стационарным компьютерам под видом характеристик энергосбережения используют высокоомную логику в ущерб качества долговечности.

На данное время есть бескулерные процессоры и видеокарты, которые явно выглядят престижнее, не уступая по производительности агрегатам, потребляющим сотни ватт. Достоинство последних можно оценить лишь в процессе длительной эксплуатации. Не зря в блоках питания ПК есть отдельная шина +5В с высоким уровнем стабилизации по стандарту. Она специально рассчитывалась изначально для логики ТТЛ и ТТЛШ. Также многие адаптеры питания в стационарной аппаратуре имеют 5-вольовую шину. Вот почему некоторые производители качественной техники всё же применяют неэкономичную и капризную в питании ТТЛ.